一文搞懂闩锁效应

AI摘要:闩锁效应是指在CMOS芯片中,由于寄生的NPN和PNP三极管相互导通,导致电源VDD和地VSS之间产生低阻抗通路,从而产生大电流,可能对芯片造成永久性损坏。文章详细介绍了闩锁效应的基础知识、形成机理、防止措施以及触发闩锁效应的常见情况。防止闩锁效应的措施包括工艺制造、版图设计和电路设计等方面。

一文搞懂闩锁效应

1. 基础知识介绍

在讲闩锁效应之前,我们要先了解下PN结和三极管的一些基础知识;

1.1 PN结相关知识

PN结正偏:

N区的电子(多数载流子)通过扩散运动,向P区注入;反之,P区的空穴(多数载流子)向N区注入;

PN结反偏(雪崩或齐纳击穿):

N区和耗尽区被碰撞电离的空穴向P区注入,P区和耗尽区被碰撞电离的电子向N区注入;

1.2 三极管相关知识

NPN和PNP导通的条件:发射结正偏,集电结反偏;

- NPN导通时,集电极收集电子;

- PNP导通时,集电极收集空穴;

Tips:理解并消化以上的相关基础知识,对后续理解Latch up形成的原因和采用相关的措施会有帮助。

2. Latch up 形成机理介绍

好了,有了上面PN结和三极管的一些基础知识,我们接下来具体说说什么是Latch up,以及形成Latch up的几种原因。

什么是Latch up?

Latch up是指在CMOS晶片中,由于寄生的NPN和PNP三极管相互导通使得在电源VDD和地VSS之间产生低阻抗通路,导致VDD和VSS之间产生大电流的一种机制。长时间的大电流将会对芯片产生永久性的损坏。

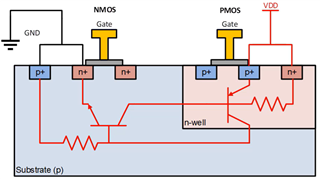

下面以CMOS中反相器(inverter)为例,详细说明Latch up产生的具体原因(寄生NPN和PNP的导通)。

图1:反相器的切面图及内部寄生三极管图

图2:内部寄生NPN和PNP的等效电路图

下面讨论寄生三级管导通的几种情况,以说明Latch up形成的具体原因。

2.1 如图1,当Vout端电位过冲(overshoot)大于VDD0.7V时;

PNP2三极管发射结正偏,又由于集电结反偏,所以此时PNP2三极管导通,此时电流通过PNP2三极管的集电极流向P-sub衬底寄生的Rpw电阻,在Rpw上形成压降,当电位超过0.7V时,使得NPN1和NPN2三极管发射结正偏,而NPN1和NPN2三极管集电结一直处于反偏,所以此时NPN1和NPN2三极管导通,使得电流进一步加大,从图2等效电路图可以明显看出,PNP(1/2)和NPN(1/2)三极管的导通,使得内部寄生三极管形成正反馈,使VDD和VSS形成低阻抗路径,最终形成大电流,烧坏芯片。

2.2 如图1,当Vout端电位远大于VDD时(类似触发ESD);

PNP2三极管导通(如情况1分析),此情况下,由于Vout端电位过高,导致nmos管漏极与P-sub衬底PN结击穿,形成热载流子效应。使得耗尽区碰撞电离产生的一大部分空穴流入P-sub衬底,形成空穴电流并在Rpw上产生电位,从而使NPN1和NPN2导通,从而进一步加大电流。导致VDD和VSS短路,形成闩锁。

2.3 如图1,当Vout端电位下冲(undershoot)小于GND 0.7V时;

分析类似 2.1节,这里不在详细描述。(建议读者自己分析有利于加深理解)。

2.4 如图1,当VSS端电位下冲小于GND 0.7V时;

由于Rpw的存在,使NPN1三极管b极电位不能瞬间变化,导致NPN1三极管发射结正偏,由于集电结反偏,所以NPN1三极管导通。此时电流通过NPN1集电结流向NW,这又导致PNP1和PNP2三极管导通,进而进一步加大电流,导致VDD和VSS短路,形成闩锁。

2.5 如图1,当VDD端电位过冲大于VDD 0.7V时;

分析类似 2.4节,这里不在详细描述。(建议读者自己分析有利于加深理解)。

说明:为简化问题分析,以上分析是假设只有其中一端发生变化,而其他端均默认不改变。然而在实际芯片中以上情况可能只发生一种也有可能是两种,但也有可能同时发生。

总结:从以上几种情况分析我们可以看出,寄生三极管的导通,其根本原因是由于外接电位的变化,先导致寄生PN结的正偏或反偏击穿,然后在Rpw和Rnw上形成压降,进而使寄生三极管导通形成正反馈,最终形成闩锁。

上面分析了形成闩锁的具体原因,那么接下来我们从不同角度来说说防止闩锁的一些主要措施。

3. 防止latch up 发生的一些措施

3.1 工艺制造角度

3.1.1 使用浅槽隔离技术

浅槽隔离,即:shallow trench isolation,简称STI。

在衬底制造器件最开始时,通过光照蚀刻等方式,在不同的器件之间形成浅的凹槽隔离,以防止不同器件之间的干扰,有较强的闩锁保护能力。

3.1.2 使用SOI工艺技术

绝缘体上硅,即:Silicon-On-Insulator,简称:SOI。

和之前工艺相比不同点是:在衬底硅和硅晶体管之间加入一层绝缘材料,形成表面硅薄层—二氧化硅绝缘材料—硅衬底的结构,使得制作的MOS管在绝缘材料上。从下图结构可以明显看出,MOS管周围全部被绝缘材料SIO2包围,因此之前的寄生三极管全部没有了,所以SOI工艺可以从根本上消除闩锁效应。

另外:SOI工艺不仅能消除闩锁效应,而且还能大幅降低寄生电容,提高器件工作速度等许多优点,所以SOI工艺也是低功耗和高性能集成电路的首选。

3.1.3 倒掺杂阱技术

从上面的分析中我们很容易知道,Rpw和Rnw电阻的大小决定了寄生三极管是否导通的主要原因。如图2,Rpw越大在寄生NPN三极管的基级电位就越高,导致NPN三极管越容易导通。反之,Rnw越大在寄生PNP三极管的基级电位就越低,导致PNP三极管越容易导通。

那么我们只要尽可能降低电阻值就可以阻止寄生三极管的导通,从而阻止闩锁发生。倒掺杂阱技术就是基于此原理,将高能量和高浓度的离子注入到阱底部(如图3),这样可以降低阱的等效电阻Rpw和Rnw,从而减小电流在阱电阻上的压降,已达到改善寄生三极管导通而形成的闩锁效应。图4,对比了传统扩散法和离子注入法杂质浓度和深度的对比图。

3.1.4 外延技术

与倒掺杂阱技术原理一样,外延技术也是通过降低体电阻Rpw来,防止闩锁效应形成。

外延技术:是将器件制作于重掺杂衬底上的低掺杂外延层中。重掺杂衬底提供一个收集电流的高传导路径,降低了Rpw;如果和倒掺杂阱技术同时使用又可以降低Rnw,从而更有效防止闩锁效应的形成。

3.2 版图设计角度

3.2.1 Guardring使用

“多子guardring”名词解释:P-Ring打在PW或Psub里一般接低电位VSS;N-Ring打在NW里一般接高电位VDD;

“少子guardring”名词解释:N-Ring打在PW或Psub里一般接高电位VDD;P-Ring打在NW里一般接低电位。

下图展示了多子和少子guardring。

从上面分析我们知道闩锁的根本原因是外接电位变化,导致寄生PN结先正偏或反偏击穿,向阱中注入载流子,然后再阱寄生电阻上形成压降,从而导致寄生三级管导通,从而形成闩锁。

那么多子和少子guardring,就是吸收PN结在正偏或反偏击穿时,向阱注入的载流子。

举例1:如上面2.2节分析,NMOS漏极和衬底形成的PN结被反向击穿,导致NMOS漏极向衬底注入空穴,此时在P-sub中的多子guardring—P-ring由于接低电位,所以能很好的吸收衬底的空穴,从而防止闩锁形;

举例2:如上面2.4节分析,NMOS源极和衬底形成的PN结正偏,导致NMOS源极向衬底注入电子,此时在P-sub中的少子guardring—N-ring由于接高电位,所以能很好的吸收衬底的电子,从而防止闩锁形;

当然为了节省面积多子guardring也同时充当衬底偏置的作用。

Tips:从图1中可以看出,寄生的PNP三极管是垂直方向的。发射极(结)发射的空穴是垂直向P衬底方向到集电极,所以即使在NW表面布局少子guardring,也起到很小的作用,故少子guardring通常放在衬底内,而不放在NW中。

3.2.2 使用足够强壮的电源线和地线,并打满Contact孔,以减小阱电阻。

3.2.3 NMOS和PMOS拉开距离。

此方式可以加宽寄生三极管NPN管的基极宽度,使得即使有电流流过阱电阻寄生的NPN三极管也很难导通,也就阻止的闩锁效应的产生。

3.3 电路设计角度

3.3.1 在电路电源或地变动较大的电路附近增加相关耦合电容,减小电源或地的波动;

3.3.2 在PAD附近增加保护二极管;

3.3.3 在电路的主通路上串联大电阻改善相关路径闩锁效应。

4. 问题与讨论

4.1 触发闩锁效应的常见的情况有哪些?

答:最常见的情况多由于外部瞬变使器件管脚的电压超过电源电压或低于地,主要包括:ESD现象、瞬时的电源干扰、电感感应回冲以及快速转换信号开关切换等。

-END-

参考资料:

- The Art of Analog Layout ,Second Edition——Alan Hastings

- CMOS 集成电路闩锁效应——温德通著

Post Views: 6,929

本文作者:WSSSS

版权声明:本作品采用CC BY-NC-SA 4.0许可,转载时须注明出处